# Advanced Computer Architecture

The Processor: Datapath and Control

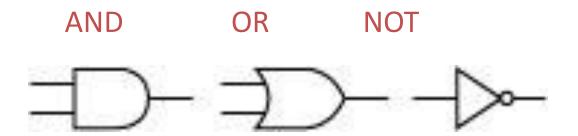

## **Logic Blocks**

- A logic block has a number of binary inputs and produces a number of binary outputs

- A logic block is termed combinational if the output is only a function of the inputs

- A logic block is termed sequential if the block has some internal memory (state) that also influences the output

- A basic logic block is termed a *gate* (AND, OR, NOT, etc.)

### Truth Table

- A truth table defines the outputs of a logic block for each set of inputs

- Consider a block with 3 inputs A, B, C and an output E that is true only if exactly 2 inputs are true

| Α | В | C | Е |

|---|---|---|---|

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

|   |   |   |   |

### Truth Table

- A truth table defines the outputs of a logic block for each set of inputs

- Consider a block with 3 inputs A, B, C and an output E that is true only if exactly 2 inputs are true

| Α | В | C | Е |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

|   |   |   |   |

### **Boolean Algebra**

- Equations involving two values and three primary operators:

- OR: symbol + , X = A + B → X is true if at least one of A or B is true

- AND : symbol . , X = A . B → X is true if both A and B are true

- NOT: symbol  $X = \overline{A} \rightarrow X$  is the inverted value of A

### Boolean Algebra Rules

- Identity law : A + 0 = A ; A . 1 = A

- Zero and One laws: A + 1 = 1; A.0 = 0

- Inverse laws : A . A = 0 ; A + A = 1

- Commutative laws: A + B = B + A ; A . B = B . A

- Associative laws : A + (B + C) = (A + B) + C

A . (B . C) = (A . B) . C

- Distributive laws : A . (B + C) = (A . B) + (A . C)

A + (B . C) = (A + B) . (A + C)

# DeMorgan's Laws

$$\bullet A.B = A + B$$

## **Pictorial Representations**

### What logic function is this?

### **Boolean Equation**

• Consider the logic block that has an output E that is true only if exactly two of the three inputs A, B, C are true

### **Boolean Equation**

Consider the logic block that has an output E that is true only if exactly two of the three inputs A, B, C are true

Multiple correct equations:

Two must be true, but all three cannot be true:

$$E = ((A . B) + (B . C) + (A . C)) . (A . B . C)$$

Identify the three cases where it is true:

$$E = (A . B . \overline{C}) + (A . C . \overline{B}) + (C . B . \overline{A})$$

### Sum of Products

- Can represent any logic block with the AND, OR, NOT operators

- Draw the truth table

- For each true output, represent the corresponding inputs as a product

- The final equation is a sum of these products

| Α | В | C | E |                                                                            |

|---|---|---|---|----------------------------------------------------------------------------|

| 0 | 0 | 0 | 0 |                                                                            |

| 0 | 0 | 1 | 0 | $(A . B . \overline{C}) + (A . C . \overline{B}) + (C . B . \overline{A})$ |

| 0 | 1 | 0 | 0 |                                                                            |

| 0 | 1 | 1 | 1 | <ul><li>Can also use "product of sums"</li></ul>                           |

| 1 | 0 | 0 | 0 | <ul> <li>Any equation can be implemented</li> </ul>                        |

| 1 | 0 | 1 | 1 | with an array of ANDs, followed by                                         |

| 1 | 1 | 0 | 1 | ·                                                                          |

| 1 | 1 | 1 | 0 | an array of ORs                                                            |

|   |   |   |   |                                                                            |

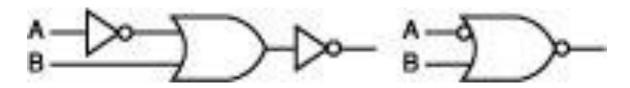

### NAND and NOR

- NAND: NOT of AND: A nand B = A.B

- NOR: NOT of OR: A nor B = A + B

- NAND and NOR are universal gates, i.e., they can be used to construct any complex logical function

# Common Logic Blocks – Decoder

### Takes in N inputs and activates one of 2<sup>N</sup> outputs

|                     | $I_1$ | l <sub>2</sub> |  |  | $O_0$ | O <sub>1</sub> | <b>O</b> <sub>2</sub> | $O_3$ | O <sub>4</sub> | O <sub>5</sub> | $O_6$ | O <sub>7</sub> |

|---------------------|-------|----------------|--|--|-------|----------------|-----------------------|-------|----------------|----------------|-------|----------------|

| 0                   | 0     | 0              |  |  | 1     | 0              | 0                     | 0     | 0              | 0              | 0     | 0              |

| 0                   | 0     | 1              |  |  | 0     | 1              | 0                     | 0     | 0              | 0              | 0     | 0              |

| 0                   | 1     | 0              |  |  | 0     | 0              | 1                     | 0     | 0              | 0              | 0     | 0              |

| 0                   | 1     | 1              |  |  | 0     | 0              | 0                     | 1     | 0              | 0              | 0     | 0              |

| 1                   | 0     | 0              |  |  | 0     | 0              | 0                     | 0     | 1              | 0              | 0     | 0              |

| 1                   | 0     | 1              |  |  | 0     | 0              | 0                     | 0     | 0              | 1              | 0     | 0              |

| 1                   | 1     | 0              |  |  | 0     | 0              | 0                     | 0     | 0              | 0              | 1     | 0              |

| 1                   | 1     | 1              |  |  | 0     | 0              | 0                     | 0     | 0              | 0              | 0     | 1              |

| 1 1 1 0 0 0 0 0 0 1 |       |                |  |  |       |                |                       |       |                |                |       |                |

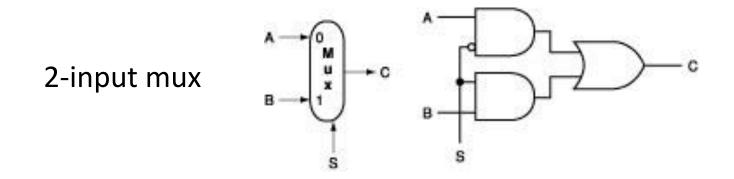

### Common Logic Blocks – Multiplexor

Multiplexor or selector: one of N inputs is reflected on the output depending on the value of the log<sub>2</sub>N selector bits

# Adder Algorithm

### Truth Table for the above operations:

| A | В | Cin | Sum Cout |

|---|---|-----|----------|

| 0 | 0 | 0   |          |

| 0 | 0 | 1   |          |

| 0 | 1 | 0   |          |

| 0 | 1 | 1   |          |

| 1 | 0 | 0   |          |

| 1 | 0 | 1   |          |

| 1 | 1 | 0   |          |

| 1 | 1 | 1   |          |

|   |   |     |          |

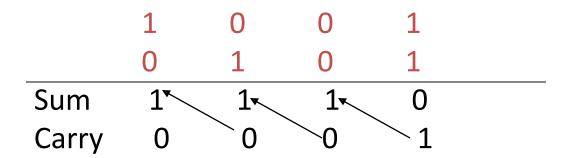

### Adder Algorithm

|       | 1   | 0 | 0 | 1 |  |

|-------|-----|---|---|---|--|

|       | 0   | 1 | 0 | 1 |  |

| Sum   | 1 🔨 | 1 | 1 | 0 |  |

| Carry | 0   | 0 | 0 | 1 |  |

### Truth Table for the above operations:

| Α | В | Cin | Sum Cout |

|---|---|-----|----------|

| 0 | 0 | 0   | 0 0      |

| 0 | 0 | 1   | 1 0      |

| 0 | 1 | 0   | 1 0      |

| 0 | 1 | 1   | 0 1      |

| 1 | 0 | 0   | 1 0      |

| 1 | 0 | 1   | 0 1      |

| 1 | 1 | 0   | 0 1      |

| 1 | 1 | 1   | 1 1      |

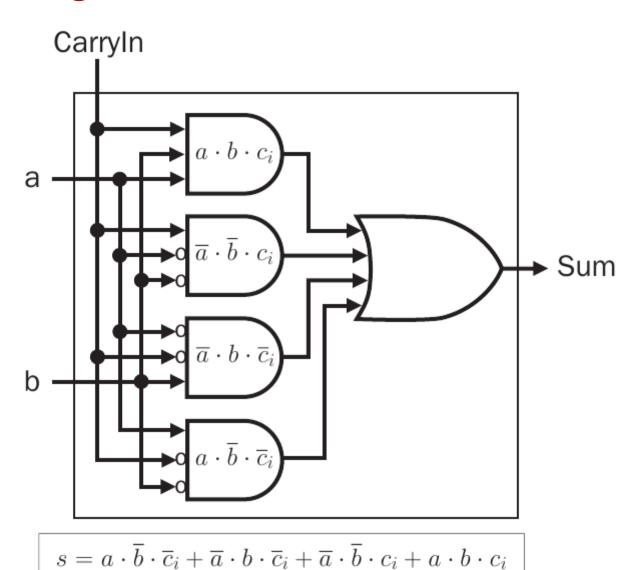

**Equations:**

$$Sum = Cin . A . B +$$

$$Cout = A . B . Cin +$$

A. Cin.

$$\overline{B}$$

+

$$B.Cin.\overline{A}$$

$$= A . B +$$

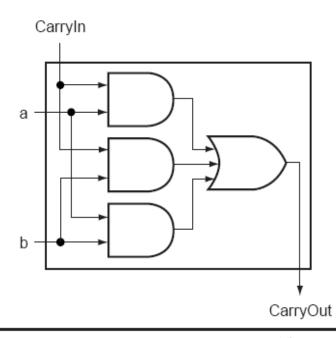

## **Carry Out Logic**

### **Equations:**

CarryOut = A . B + A . Cin + B . Cin

**FIGURE B.5.5** Adder hardware for the carry out signal. The rest of the adder hardware is the logic for the Sum output given in the equation on page B-28.

## The Sum Logic

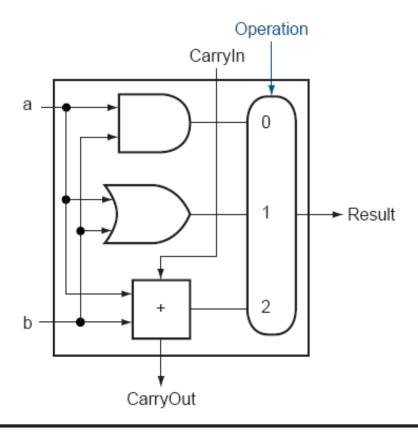

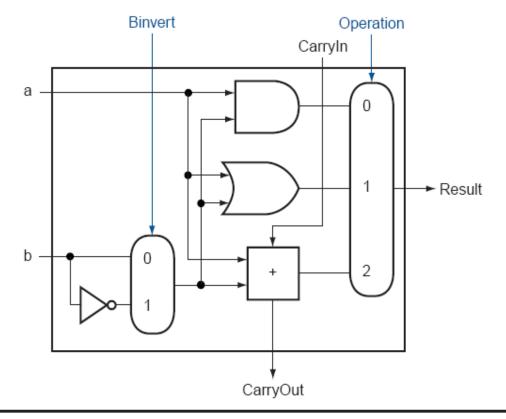

### 1-Bit ALU with Add, Or, And

Multiplexor selects between Add, Or, And operations

FIGURE B.5.6 A 1-bit ALU that performs AND, OR, and addition (see Figure B.5.5).

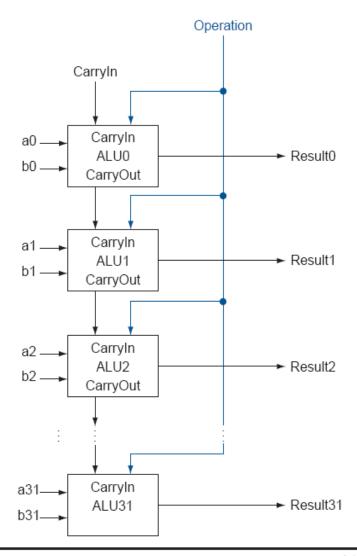

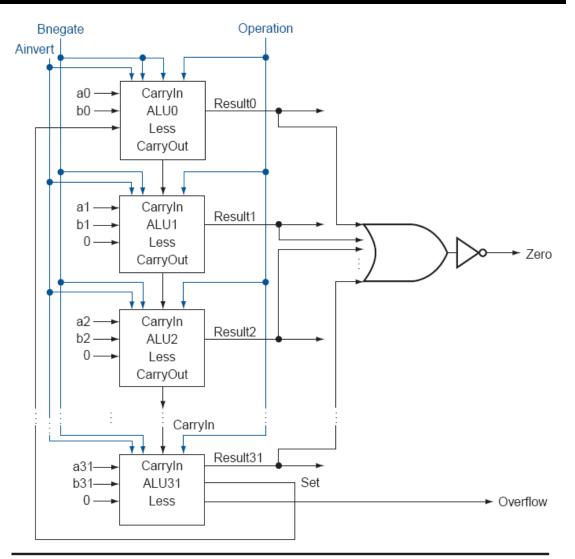

## 32-bit Ripple Carry Adder

1-bit ALUs are connected "in series" with the carry-out of 1 box going into the carry-in of the next box

**FIGURE B.5.7** A **32-bit ALU constructed from 32 1-bit ALUs.** CarryOut of the less significant bit is connected to the CarryIn of the more significant bit. This organization is called ripple carry.

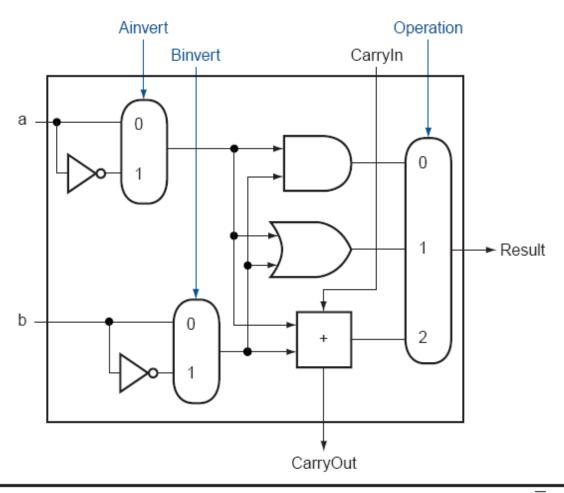

# **Incorporating Subtraction**

### **Incorporating Subtraction**

#### Must invert bits of B and add a 1

- Include an inverter

- CarryIn for the first bit is 1

FIGURE B.5.8 A 1-bit ALU that performs AND, OR, and addition on a and b or a and  $\overline{b}$ . By selecting  $\overline{b}$  (Binvert = 1) and setting CarryIn to 1 in the least significant bit of the ALU, we get two's complement subtraction of b from a instead of addition of b to a.

# **Incorporating NOR**

### **Incorporating NOR**

FIGURE B.5.9 A 1-bit ALU that performs AND, OR, and addition on a and b or  $\overline{a}$  and  $\overline{b}$ . By selecting  $\overline{a}$  (Ainvert = 1) and  $\overline{b}$  (Binvert = 1), we get a NOR b instead of a AND b.

### **Control Lines**

What are the values of the control lines and what operations do they correspond to?

**FIGURE B.5.12** The final **32-bit ALU.** This adds a Zero detector to Figure B.5.11.

### **Control Lines**

What are the values of the control lines and what operations do they correspond to?

|     | Ai | Bn | Op |

|-----|----|----|----|

| AND | 0  | 0  | 00 |

| OR  | 0  | 0  | 01 |

| Add | 0  | 0  | 10 |

| Sub | 0  | 1  | 10 |

| SLT | 0  | 1  | 11 |

| NOR | 1  | 1  | 00 |

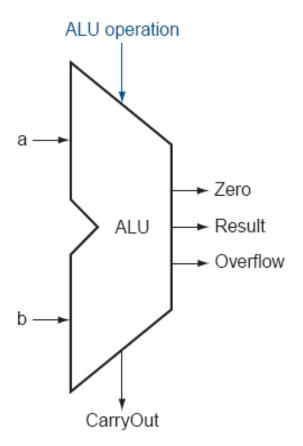

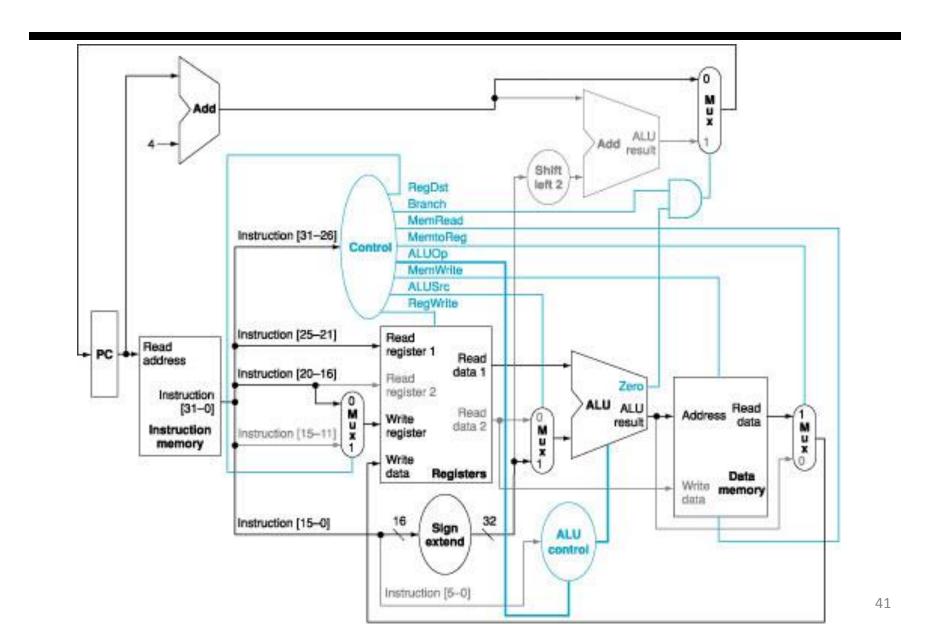

### **Basic MIPS Architecture**

- We'll design a simple CPU that executes:

- basic math (add, sub, and, or, slt)

- memory access (lw and sw)

- branch and jump instructions (beq and j)

### Implementation Overview

- We need memory

- to store instructions

- to store data

- for now, let's make them separate units

- We need registers, ALU, and a whole lot of control logic

- CPU operations common to all instructions:

- use the program counter (PC) to pull instruction out of instruction memory

- read register values

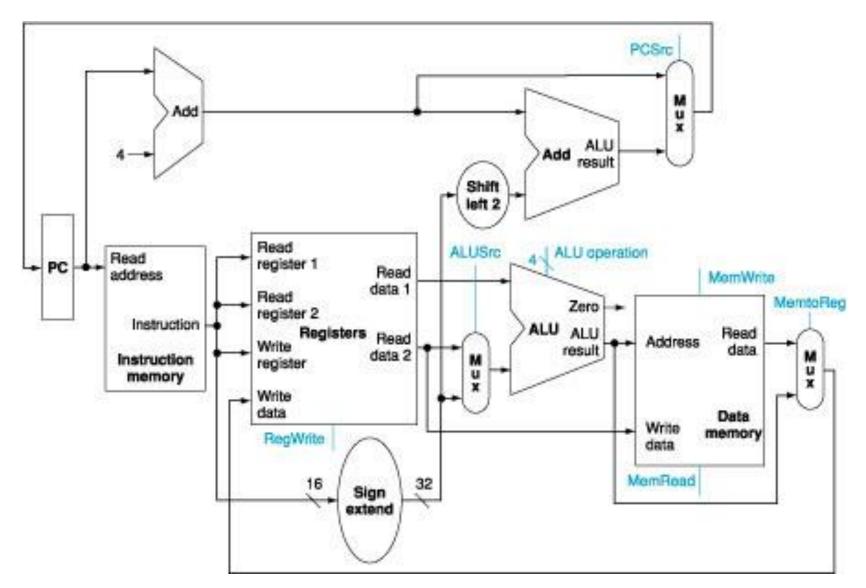

### Datapath

• Datapath Element: A functional unit used to operate or hold data within the processor. Examples in MIPS implementation are memory, register file, ALU and adders.

Datapath: Collection of all datapath elements

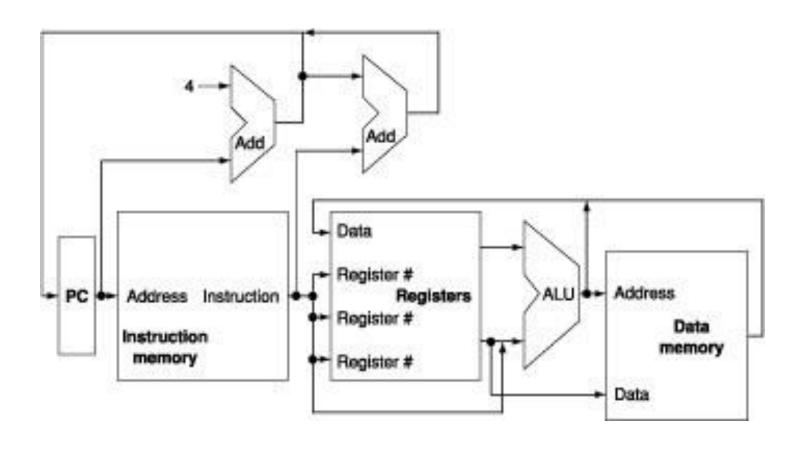

### An Overview of the Architecture

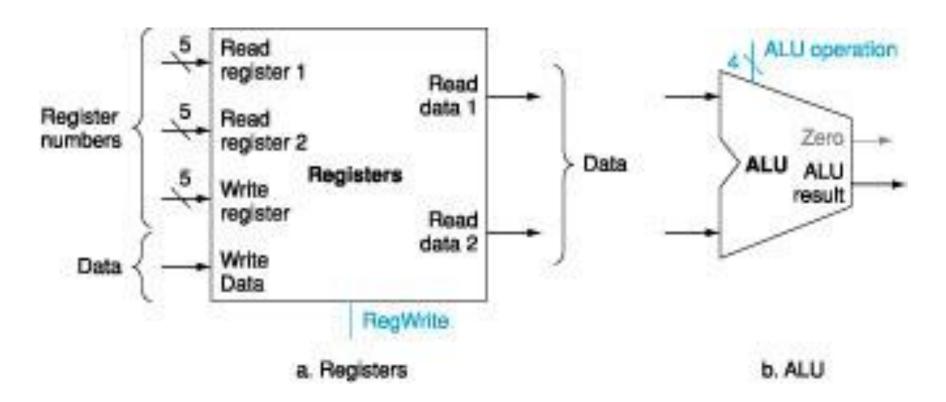

### Implementing R-type Instructions

• Instructions of the form add \$t1, \$t2, \$t3

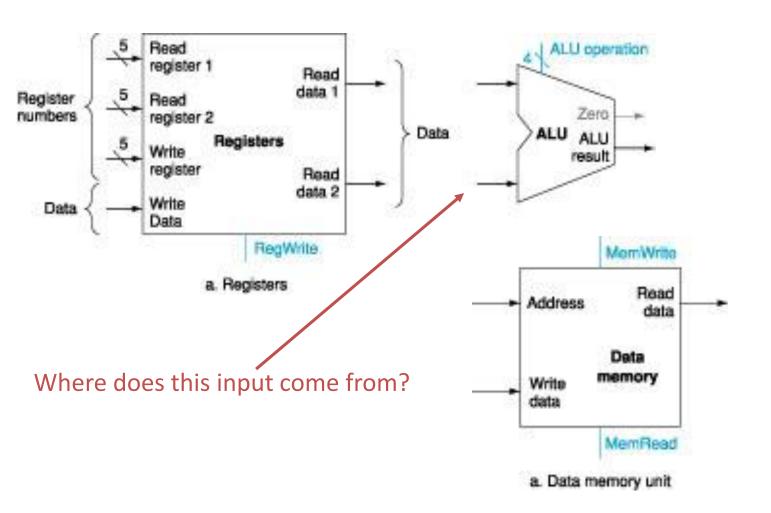

# Implementing Loads/Stores

• Instructions of the form lw \$t1,8(\$t2) and sw \$t1,8(\$t2)

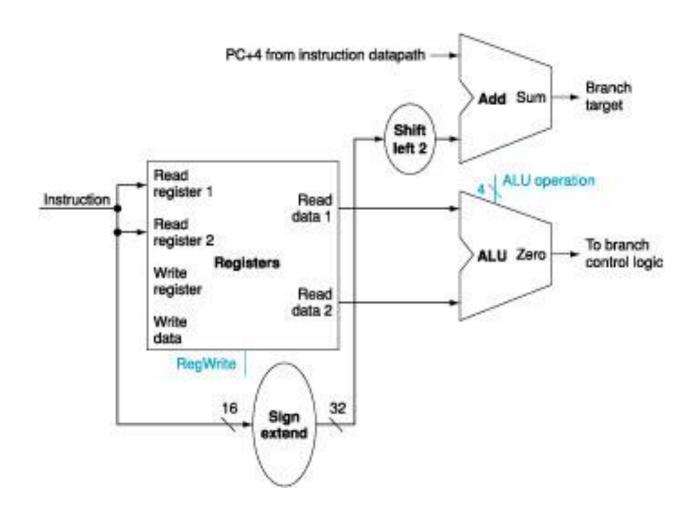

### Implementing J-type Instructions

• Instructions of the form beq \$11, \$12, offset

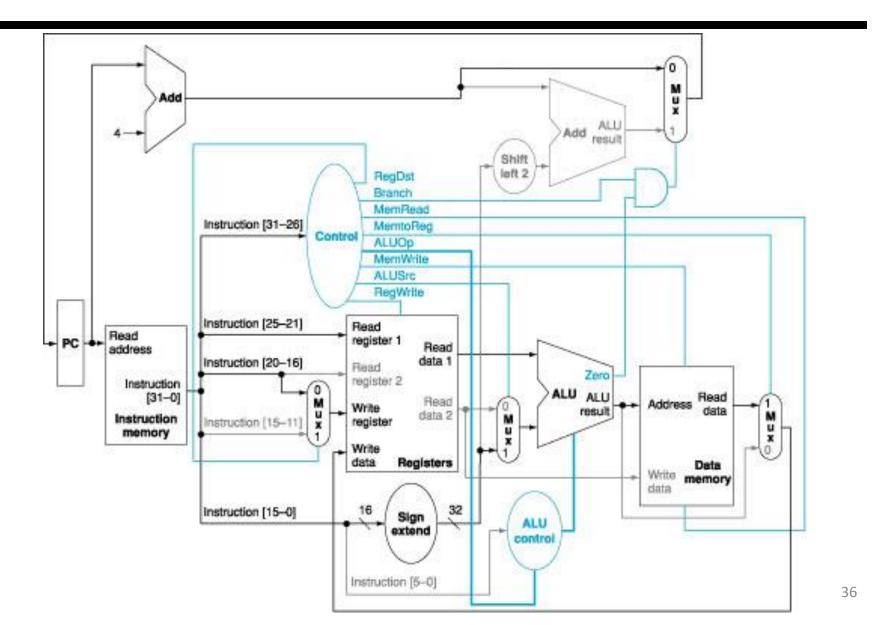

# Adding Control Signals to the Datapath

# Adding Control Unit to the Datapath

### Reviewing the R Type and I Type Format

```

R-type instruction add $t0, $s1, $s2

000000 10001 10010 01000 00000 100000

6 bits 5 bits 5 bits 5 bits 5 bits 6 bits

op rs rt rd shamt funct

opcode source source dest shift amt function

```

```

I-type instruction6 bits5 bits5 bits16 bitsopcodersrdconstant

```

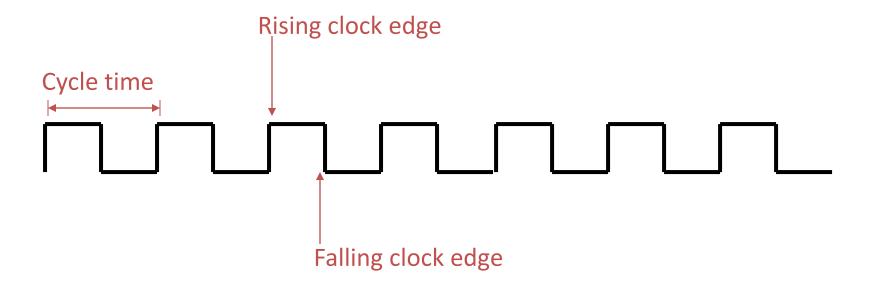

## **Clock Terminology**

$$4 \text{ GHz} = \text{clock speed} = \underbrace{1}_{\text{cycle time}} = \underbrace{1}_{\text{cycle time}}.$$

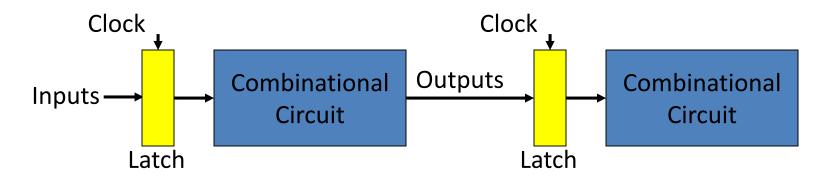

### **Sequential Circuits**

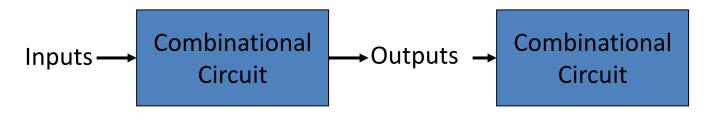

Until now, circuits were combinational – when inputs change, the outputs change after a while (time = logic delay through circuit)

We want the clock to act like a start and stop signal – a "latch" is a storage device that stores its inputs at a rising clock edge and this storage will not change until the next rising clock edge

### **Sequential Circuits**

- Sequential circuit: consists of combinational circuit and a storage element

- At the start of the clock cycle, the rising edge causes the "state" storage to store some input values

- This state will not change for an entire cycle (until next rising edge)

- The combinational circuit has some time to accept the value of "state" and "inputs" and produce "outputs"

- Some of the outputs (for example, the value of next "state") may feed back (but through the latch so they're only seen in the next cycle).

- Determine the <u>clock rate</u> for the MIPS architecture, assuming the following:

- The MIPS is a Single Cycle Machine

- 1 clock cycle per instruction

- CPI = 1

- Access time for memory units = 200 ps

- Operation time for ALU and adders = 100 ps

- Access time for register file = 50 ps

| <b>Instruction Class</b> | F           | Functional Units used by the Instruction Class |     |          |          |  |  |  |

|--------------------------|-------------|------------------------------------------------|-----|----------|----------|--|--|--|

| ALU Instruction          | Inst. Fetch | Register                                       | ALU | Register |          |  |  |  |

| Load Word                | Inst. Fetch | Register                                       | ALU | Memory   | Register |  |  |  |

| Store Word               | Inst. Fetch | Register                                       | ALU | Memory   |          |  |  |  |

| Branch                   | Inst. Fetch | Register                                       | ALU |          |          |  |  |  |

| Jump                     | Inst. Fetch |                                                |     |          |          |  |  |  |

| <b>Instruction Class</b> | Instr<br>Memory | Register read | ALU operation | Data<br>Memory | Register<br>write | Total  |

|--------------------------|-----------------|---------------|---------------|----------------|-------------------|--------|

| ALU Instruction          | 200             | 50            | 100           | 0              | 50                | 400 ps |

| Load Word                | 200             | 50            | 100           | 200            | 50                | 600 ps |

| Store Word               | 200             | 50            | 100           | 200            | 0                 | 550 ps |

| Branch                   | 200             | 50            | 100           | 0              | 0                 | 350 ps |

| Jump                     | 200             | 0             | 0             | 0              | 0                 | 200 ps |

- The clock cycle time for a machine with a single clock cycle per instruction will be determined by the longest instruction.

- In this example, the <u>load word</u> instruction requires 600 ps.

- The clock rate is then

```

Clock rate = 1 / Clock Cycle Time

```

Clock rate = 1 / 600 ps = 1.67 GHz

# Performance Issues

- Longest delay determines clock period

- Critical path: load word (lw) instruction

- Instruction memory → register file → ALU → data memory → register file

- Improve performance by <u>pipelining</u>